Interfaz PSoC 5LP con FPGA

Saludos lectores, en esta entrada les hablaremos

sobre un proyecto de la clase de Electrónica II.

Introducción:

Algunos dispositivos electrónicos no pueden leer

señales analógicas, y la mayoría de los sensores manejan a su salida este tipo

de señales, por lo que es útil tener algún dispositivo externo para convertir

señales analógicas a digitales para poder manejarlas.

Objetivo: Interfaz entre PSoc y FPGA.

Leer la señal de un sensor de temperatura LM35 con

ayuda del PSoc 5LP y transmitir esa

información a una tarjeta FPGA (Basys 2) la cual leerá esa información y

mostrara la temperatura.

Procedimiento:

Crear un nuevo proyecto en el PScoC Creator,

seleccionando “PSoC 5LP Design”

Seleccionar nuestro dispositivo correspondiente.

Agregar al diseño esquemático lo siguiente.

Convertidor Analógico-Digital (SAR ADC, en este caso)

Un control de registros (“Control Register”)

Un Pin análogo (“Analog Pin)

Varios Pines Digitales (se pueden configurar Digital

Input/Output)

Conexiones.

Conectar el pin análogo a la entrada del ADC.

(Esto es para mandar la señal del sensor al pin

analógico y de ahí conectarlo a nuestro ADC del PSoc. El ADC deberá estar

configurado en 8 bits (Como se muestra en la figura 1).

Configurar el control de registros con 8 pines (Como se aprecia en la figura 2).

|

| Figura 2 – Control de registros con 8 salidas. |

Conectar los pines de salida del control de

registros a los pines digitales, pero aquí tenemos que tomar en cuenta que la

salida normal de los pines digitales (un HIGH) es de 5V, y como en este

proyecto usaremos una FPGA que solo admite en sus entradas 3.3V tenemos que

adecuar esas salidas. Lo que se aplicó en este ejemplo fue configuras la salida

de los pines referenciados (como se puede observar en la figura 3), para esto ocupamos

otro pin analógico conectado 3.3V.

|

| Figura 3 – Salidas de pines digitales referenciadas. |

Ya con todo conectado podemos observar el esquema

completo (figura 4) donde el LM35 fue solamente ilustrativo para que se

aprecien mejor las conexiones, y por comodidad, configuramos los pines

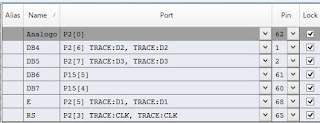

digitales con dos pines (figura 5), el orden de las conexiones de la salida del

control de registros lo adecuamos para que concuerde con en el orden del

programa en la Basys 2 (en este caso el bit más significativo era el pin 12(0)

en el PIN_2)

|

| Figura 4 – Esquema completo |

Código.

En esta parte lo más importante es leer una variable

“N” que será el valor de bits de 0 a 255, pero como la salida máxima del LM35

es de 1.5V agregamos en el código una ganancia para que el rango vaya de

acuerdo al de nuestro ADC que es de 0 a 5 V es decir de 0 a 255 bits. El código

empleado se puede observar en la figura 6.

|

| Figura 6 – Código empleado para el programa |

Ya finalizando las pruebas en protoboard y

verificando que todo funcione correctamente procedimos a realizar la placa fenólica,

la interfaz ya conectada y funcionando se puede apreciar en la figura 7.

|

| Figura 7 – Interfaz conectada y funcionando |

Es importante mencionar que a la hora de realizar las pruebas, probando las salidas del control de registros, nos encontramos con un detalle que causaba problemas, la salida del Pin 12(6), sin importar el orden que le diéramos, sacaba mal el voltaje, es decir colocando en el código que el ADC escribiera 0 bits, deberíamos tener 0V en las 8 salidas, pero ese pin ya mencionado sacaba .4V y en el momento de probar que escriba 255 bits donde deberíamos ver las 8 salidas en 3.3V ese mismo pin mostraba 3.9V y como ya habíamos mencionado eso nos causaría problemas en el FPGA, lamentablemente no logramos encontrar a que se debía esta variación, así que la solución que se le dio fue conectarle en serie un diodo (que consume aproximadamente .7V) para atenuar ese voltaje de 3.9V y una resistencia a tierra, para evitar ruidos y problemas que causaría tenerlas conectadas al aire, entonces después del diodo, conectamos la salida de ese pin y de ahí a la Basys 2.

Aquí les dejamos un vídeo del proyecto funcionando.